# Performance Analysis of Cascaded Multi-level Inverter Fed Induction Motor

Sudhi Sikarwar<sup>1</sup>, Ranjeeta Khare<sup>2</sup>

<sup>1</sup>Research Scholar, EX Deptt. OCT, Bhopal, <sup>2</sup> Professor, EX Deptt. OCT, Bhopal

Abstract - Today's multilevel inverters have become very important topology for ac drives. Multi-level voltage source inverter technology has emerged as an important alternative in the control of high power medium voltage energy. The main purpose of this paper is to compare different cascaded multilevel inverter fed induction motor. This paper also describes the comparison between harmonics distortion values, a voltage and current waveforms of induction motor. More over it can also be used for charged balance controlled amongst the multiple input DC sources in a given topology multilevel voltage source inverters have various advantages: Reduction in electromagnetic interference, reduction in the voltage rating of the power semiconductor switching devices, for better output voltage having reduced total harmonic distortion. Here we analysis the different firing scheme for cascade H-Bridge multilevel inverter.

Keywords – Cascade H-Bridge multilevel inverter, Total harmonic distortion (THD), CPWM, PD, POD, AOPD, Induction motor.

#### I. INTRODUCTION

In recent year many industrial drive use ac induction motor because induction motor is less expensive and reliable generally induction motor is used for constant speed but now a day's induction motor is also used for variable speed with the help of power electronics devices. These electronics devices not only improve the speed of motor but it can also improve the steady and dynamic characteristics of motor. There are various schemes such as PWM, SPWM, SVPWM, CPWM. etc. for controlling multilevel inverter like diode clamp inverter, capacitor clamp inverter, cascading H-bridge multilevel inverter for achieving dynamics performance of induction motor. In this paper we use cascade H-Bridge multilevel inverter for controlling induction motor.

- It produce output voltage with low distortion and lower dv/dt.

- 2) They draw input current with very low distortion.

- 3) It generates smaller common mode voltage for reducing the stress of the motor load.

- 4) It can operate with a lower switching frequency.

In recent year industry require higher power which is reached in megawatt. For working with higher voltage we introduce multi-level inverter to control ac drives. Such as diode clamp inverter, capacitor clamp inverter and cascaded H-Bridge multilevel inverter. In this paper we briefly discuss about cascaded H-Bridge multi level inverter.[1],[6]

## II. CASCADE H-BRIDGE MULTILEVEL INVERTER

Cascade H-Bridge multilevel is better than other multilevel inverter because its structure is simple. It requires less switching components. Cascade H-Bride multilevel inverter is the group of capacitor and switches.[15]

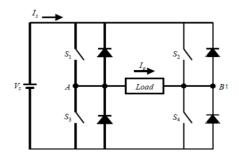

Fig. 1 Cascading H-Bridge MLI

In the above fig1. The circuit diagram of cascading H-Bridge multilevel inverter. Cascading H-Bridge multi level inverter is most important topology in the multilevel inverter. It gives a desire AC voltage from several DC input voltage it require less number of component as compare to diode clamp inverter and flying capacitor inverter each H-Bridge multilevel inverter produce three level of voltage Vdc, 0, -Vdc by different combination of four switches S1, S2, S3 and S4 .then the magnitude of ac output voltage will be.

$$V0 = V01 + V02 + V03 + Von -----(1)$$

Switching pattern of cascade H-Bridge multilevel inverters shown below.

Table no. 1 Switching table for cascade H-Bridge MLI

| V0 = Van | <b>S</b> 1 | S2 | <b>S</b> 3 | S4 |

|----------|------------|----|------------|----|

| Vdc      | 1          | 0  | 0          | 1  |

| 0        | 1          | 1  | 0          | 0  |

| 0        | 0          | 0  | 1          | 1  |

| - Vdc    | 0          | 1  | 1          | 0  |

#### **Cascaded N-level inverter:**

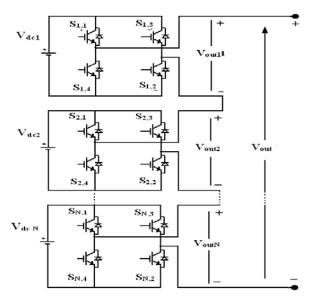

A cascaded N-Level inverter consist of a number H-

Bridge inverter with separate dc source for each unit and connected in series as shown in fig.2. Each h-Bridge can be produce three level of voltage namely +Vdc, 0, and -Vdc.

Fig2. Block diagram of cascaded N-Level inverter

For symmetric inverter all dc voltage sources equal to Vdc, the number of available voltage step level is:

$N_{step} = 2n + 1$  (2)

Where n represented the number of full-bridges and maximum output voltage will be:

$V_{omax} = n \times V dc$ ------(3)

There are following advantage of cascading H-Bridge multilevel inverter:

(1)It reduces total harmonic distortion.

(2)It requires less number of components for each level.

(3)It is more flexible than other multilevel inverter.

(4)Its circuit is simple and reliable.

## **Disadvantage:**

The main disadvantage of cascading H-Bridge multi inverter is it requires separate DC voltage sources.

## III. CONTROL SCHEME FOR MULTILEVEL INVERTER

There are following method for controlling the multi level inverter discussed below.

(a)Pulse width modulation technique (PWM).

(b)Sinusoidal Pulse width Modulation(SPWM).

(C)Third harmonics pulse width modulation (THI-PWM).

(d)Space vector pulse width modulation (SPPWM)

(e)Selective Harmonic Elimination Method (SHE-PWM).

#### Pulse width modulation control:-

This method is most popular method of controlling the output voltage, in this method a fixed dc input voltage is given is given to the inverter and controlled ac output voltage is obtained by adjusting the off periods of the inverter components. [17-19]

There are following advantage of pulse width modulation

- (1) The output voltage control with this method can be obtained without any additional components.

- (2) With this method lower order harmonics can be eliminated or minimized along with its output voltage control. As higher order harmonics can be filtered easily, the filtering requirements are minimized.

#### Space vector pulse width modulation:

In a conventional two level multilevel inverter the harmonics reduction in the output current of inverter is computed by increasing the switching frequency however in high power applications the switching frequency of the power device is restricted below 1kHz because of increasing switching losses and level of dc voltage. While the very high dv/dt which is generated with high DC link voltage is the cause for electromagnetic interference and motor winding stress. There for from the harmonic reduction and high DC – link voltage level point of view multilevel inverters are more suitable.

Much has been worked on the space vector modulation of multilevel inverter. In SVPWM method the output voltage is presented in three dimensional Euclidean space. The principle of this method is that increase in the number of level by one allows forms and additional hexagonal rings of equilateral triangles which surrounds the outermost hexagon. The hexagon which represent space vector diagram is flatten and reference voltage vector is normalize so that the computation of the algorithm is reduce.

A SVPWM has a predictive current control loop in this load the current is determined for all output voltage vectors of the inverters. The calculation of current error and selection of switching state is done when the value of error is less. A SVM causes reduction in the inverter output voltage distortion because of turn OFF, turn ON and dead times of power modules without increasing the harmonics content.[9-11],

The reference vector can be written as

$V = (T_1 V_n + T_2 V_{n+1})/T_s - \dots - (4)$

Whereas  $T_1$ ,  $T_2$  are applied effective times corresponding to the active vectors  $V_1 - V_6$ .

The effective time can be calculated as follows

$$T_{1} = \nabla T_{s} \sin(\pi/3 - \alpha) / \nabla dc 2/3 \sin(\pi/3) - ....(5)$$

$$T_{2} = \nabla T_{s} \sin(\alpha) / \nabla_{dc} 2/3 \sin(\pi/3) - ...(6)$$

$$T_{0} = T_{s} - T_{1} - T_{2} - ...(7)$$

Where  $T_0$  is the time corresponding to null vector  $V_{dc}$  is the DC linkage voltage and  $T_s$  is the sampling time.

## Multicarrier Sine-PWM :-

Multilevel carrier based PWM method have triangular waves or saw tooth waves multiple carrier signals show freedom in following characteristics – frequency, amplitude, face of each carrier and offset between the carriers. The reference wave can be either sinusoidal or trapezoidal. A reference wave two shows freedom in parameters like frequency, amplitude, phase angle, and injection of zero sequence signal to it. Hence many multilevel carrier based PWM methods, using these combinations may be obtained.[27], [33],

The carrier based Schemes can be classified as:

(a)Level shift PWM (LSPWM)

(b)Phase shifted PWM (PSPWM)

(C)Hybrid (H)

## Level shift PWM

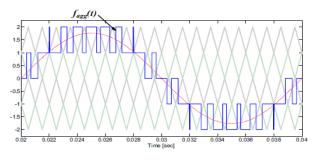

(1)Alternative phase opposition disposition (APOD) – In alternative phase opposition disposition the carrier signals are out of phase by  $180^{\circ}$ .

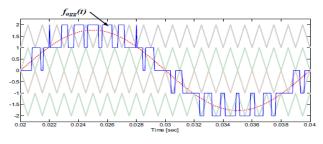

Fig.3 carrier signal waveform of alternative phase opposition disposition

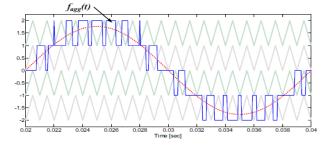

(2)Phase disposition (PD) : - In phase disposition the carrier signals are in phase.

Fig. 4 Carrier signal wave of phase disposition

(3)**Phase opposition disposition** (**POD**) - in POD the carrier signals are all in phase above and below the zero reference but phase difference of 180°.

Fig.5 carrier signal wave of phase opposition disposition

#### Phase shifted PWM -

In phase shifted PWM carrier signals have same amplitude and all are phase shifted.

#### Hybrid H-

The hybrid is the combination of phase shifted and level shifted technique.

**Sinusoidal pulse width modulation (SPWM)**:- The SPWM technique provides the way for pushing the predominant harmonics to a high frequency. In SPWM technique the comparison between the carrier signal of high frequency and modulating signal of the desired frequency can be easily done. Increasing the switching frequency leads to deduction in lower order harmonics from the output Voltage.

$V_{m} = m \sin(\omega + j 2\pi/3) - ....(6)$   $m = A_{m}/A_{u1} + A_{u2} + A_{11} + A_{12} - ....(7)$  $m_{f} = f_{c}/f_{m} - ....(8)$

where j = 0, -1, +1 x = a, b, c,

$\label{eq:main} \begin{array}{l} m = modulation index, \ mf = frequency \ ratio, \ f_c = \\ carrier \ wave \ frequency, \ f_m = modulating \ wave \ frequency, \\ A_m = modulating \ wave \ to \ peak \ amplitude, \ A_{u1}, \ A_{u2}, \ A_{11}, \\ A_{12} = upper1, \ upper2, \ lower1 \ and \ lower2 \ carrier \ waves \\ peak \ -to-peak \ amplitudes. \end{array}$

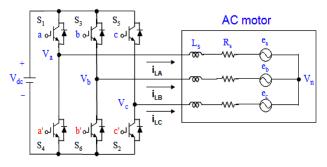

The fig 5(b) shows three phase bridge inverter fed induction motor.

Fig.5 (b) Bridge inverter

## IV. SIMULATION RESULTS

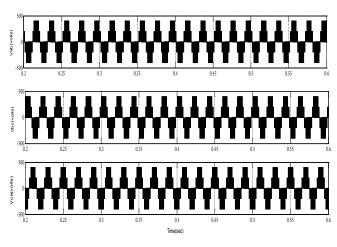

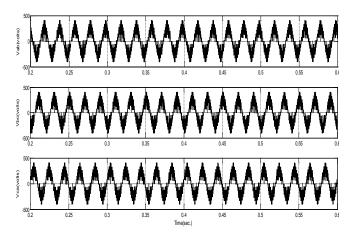

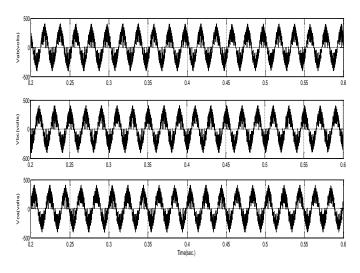

Fig. 6 show the output line to line voltage waveform of three level cascaded H-Bridge multilevel inverter.

Fig.6 Three-level cascaded H-Bridge line to line voltage waveform.

Fig. 7 show the output line to line voltage waveform of five level cascaded H-Bridge multilevel inverter.

Fig.7 Five-level cascaded H-Bridge line to line voltage waveform.

Fig. 8 show the output line to line voltage waveform of seven level cascaded H-Bridge multilevel inverter.

Fig.8 Seven-level cascaded H-Bridge line to line voltage waveform.

Fig. 9 show the output line to line voltage waveform of nine level cascaded H-Bridge multilevel inverter.

## Fig.9 Nine-level cascaded H-Bridge line to line voltage waveform.

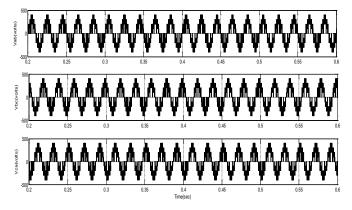

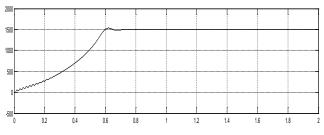

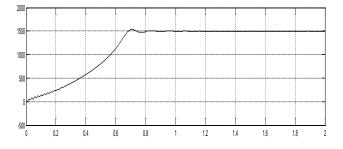

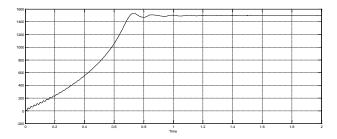

Fig.10 Show the rotor speed of induction motor fed by cascaded three level H-Bridge inverter. The speed will remain constant at 1480rpm.

Fig10.Rotor speed of cascaded three level inverter fed induction motor

Fig.11 Show the rotor speed of induction motor fed by cascaded five-level H-Bridge inverter. The speed will remain constant at 1480rpm.

Fig11. Rotor speed of cascaded five level inverter fed induction motor.

Fig.12 Show the rotor speed of induction motor fed by cascaded seven-level H-Bridge inverter. The speed will remain constant at 1480rpm.

Fig.12 Rotor speed of cascaded seven level inverter fed induction motor.

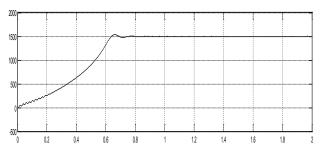

Fig.13 Show the rotor speed of induction motor fed by cascaded nine level H-Bridge inverter. The speed will remain constant at 1480rpm.

Fig.13 Rotor speed of cascaded nine level inverter fed induction motor.

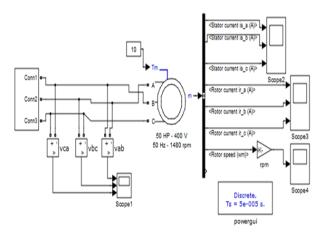

Fig.14 shows the simulation model of nine-level inverter fed induction motor drives. Where  $I_a,\,I_b$  and  $I_c$  is the line

current and  $V_{ab}$ ,  $V_{bc}$ ,  $V_{ca}$  is the line voltage and we analyze the performance of the motor at different level of inverter.

Fig.14. Nine-level inverter circuit fed induction motor simulation model.

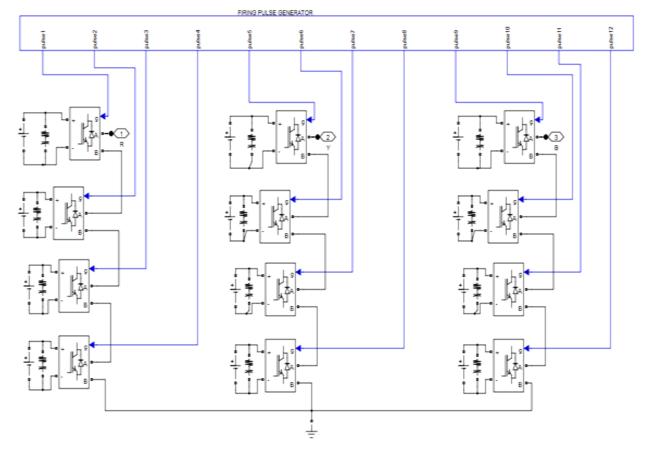

Fig.15 shows the simulation model of cascaded nine-level inverter and the PWM circuit to generate the gating signals for the multilevel inverter switches.

Fig.15 Simulation model of cascaded nine-level inverter.

The % total harmonic distortion of cascaded line inverter voltage is shown in table no.2

| Level       | THD    |

|-------------|--------|

| Three level | 11.06% |

| Five level  | 8.94%  |

| Seven level | 5.64%  |

| Nine level  | 5.36%  |

#### Table2.(%THD value)

#### V. CONCLUSION

A comparative analysis of total harmonics output line to line voltage of three-level, five-level, seven-level, and nine-level cascaded H-Bridge multilevel inverters fed with induction motor is presented in this paper. It is observed that the level of inverter increase there is an improvement in the performance of induction motor. The total harmonics distortion of line to line voltage and phase current decrease with increase in the levels of inverter.

## VI. REFERENCES

- Jose Roriguez, and Fang Zheng Peng, , "Multilevel inverters: A Survey of Topologies, Controls, and Applications" IEEE conf., 2002.

- [2] P.Palanive and Subhransu Sekhar Dash, "Multicarrier Pulse Width Modulation Methods Based Three Phase Cascaded Multilevel Inverter Including Over Modulation and Low Modulation Indices" conf IEEE 2009

- [3] Kfir J.Dagan, Raul Rabinovici and Dmitry Baimel, "An Analytical Approach to Total Harminics Distortion Reduce in Multi-Level Inverters" cof. IEEE 2010

- [4] Rokan Ali Ahmed, S.Mekhilf, and Hew Wooi Ping, "New multilevel inverter topology with minimum number of switches". Conf IEEE 2010.

- [5] Bernardo Cougo, Guillaume Gateau and Malgorzata, "PD Modulation Scheme for Three-Phase Parallel Multilevel Inverters" cof. IEEE2011.

- [6] Arif-Judi, Hussain Bierk and Ed Nowicki, "Selective Harmonic Power Optimization in Multilevel Inverter" conf IEE 2011.

- [7] A. Nabae, I. Takshashi, and H. Akagi, "A new neutral-poin clamped PWM inverter," IEEE Trans. Ind. Applicat, oct 1981.

- [8] J.S Lai and F.z. Peng, "Multilevel converters- A new bread of power converter," IEEE may1996.

- [9] N. Celanovic and D.Boroyevich, "A space vector modulation algoritm for multilevel three phae converter, IEEE appl 2001.

- [10] C.Attaainse, V.Nardi, and G.Tomasso, "space vector modulation algorith for power losses and THD reduction in

VSI based drives," Elecrical power components and system, pp1271-1283,2007.

- [11] Anees Mohamed, A.S.Anish Gopinath, and M.R. Baiju," Asimple space vector PWM generation schime for any general n-level inverter, IEEE trans May 2009.

- [12] G.Mondal, "A Reduced –Switch-Count Five-Level inverter With Comman-Mode Voltage Eliminition for an Open –End Winding Induction motor drives " IEEE Transactions on Industrial Electronics, pp.2344-2351, 2007

- [13] Najaf, E.Yatim ,"Design and implementation of a new multilevel inverter topology, "Industrial Electronics, IEEE Transaction on, vol pp 01-99.

- [14] Rodriguez, j. Bernet, S.STEIMER, P.K. and Lizama, "Asurvey on neutral-point-clamped inverters," IEEE Trans.Ind.Electron, vol 57. Pp. 22192230, jul.2010.

- [15] M. Malinowski, K.Gopakumar, J.Rodriguez, and M.Perez, "A survey on cascaded multilevel inverters," IEEE Trans. On Industrial Electronics, IEEE ., PP2197-2206, JUL.2010.

- [16] J. Wang, Y.Huang ang F.Z.Peng "A practical Harmonics Elimination Method for Multilevel Inverters" IEEE conf Industrial application, 6oct 2005, pp. 1665-1670.

- [17] S. Ogasawara, H. Akagi, and A. Nabae, "A novel PWM scheme of voltage source inverters based on space vector theory," in *Proc. EPE*, Aachen, Germany, Oct. 1989, pp. 1197–1202.

- [18] V. Blasko, "Analysis of a hybrid PWM based on modified space-vector and triangle-comparison methods," *IEEE Trans. Ind. Appl.*, vol. 33, no. 3, pp. 756–764, May/Jun. 1997.

- [19] Amit kumar gupta and Ashwin M.Khambadkone, "A general space vector PWM Algorithm for Multilevel inverters, including operation in over – modulation Range," IEEE Trans. Power Electronics, vol.22, pp517-526, March 2007.

- [20] J. Rodriguez, J.S. Lai, Fang Z. Peng, "Multilevel Inverters: A Survey of Topologies, Controls and Applications," *IEEE Trans on Industrial Electronics*, vol.49, no.4, pp 724-738 Aug 2002.

- [21] N.S. Choi, J.G.Cho, and G.H.Cho, "A general Circuit topology of multilevel inverter," *in Proc. IEEE PESC'91*, 1991, pp.96-103.

- [22] Zhang, A.V. Jouanne, Shaoan Dai, A.K.Wallace and F.Wang, "Multilevel Inverter Modulation Schemes to Eliminate Common-Mode Voltages," *IEEE Trans on Ind. Appl*, vol. 36, no 6, pp 1645- 1653 Nov/Dec 2000.

- [23] Jose, Steffen Sernet, Bin Wu, Jorge and SamirKouro, "Multilevel Voltage Source Converter Topologies for Industrial Medium Voltage Drives," *IEEE Trans on Industrial Electronics*, vol.54, no.6, Dec 2007.

- [24] M. P. Steimer and J. K. Steinke, "Five level GTO inverters for large induction motor drives," in *Conf. Rec. IEEE-IAS Annu. Meeting*, Oct.1993, pp. 595–601.

- [25] F. Z. Peng, J. S. Lai, J.W. McKeever, and J.VanCoevering, "A multilevel voltage-source inverter with separate DC sources for static var generation," *IEEE Trans. Ind. Applicat.*, vol. 32, pp. 1130–1138, Sept. 1996.

- [26] D. G. Holmes and B. P. McGrath, "Opportunities for harmonic cancellation with carrier-based PWM for twolevel and multilevel cascaded inverters," *IEEE Trans. Ind. Applicat.*, vol. 37, pp. 574–582, Mar./Apr. 2001.

- [27] L. Li, D. Czarkowski, Y. Liu, and P. Pillay, "Multilevel space vector PWM technique based on phase-shift harmonic suppression," in *Proc. IEEE APEC*, New Orleans, LA, Feb. 2000, pp. 535–541.

- [28] F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," *IEEE Trans. Ind. Applicat.*, vol. 37, pp. 611–618, Mar./Apr. 2001.

- [29] V. G. Agelidis and M. Calais, "Application specific harmonic performance evaluation of multicarrier PWM techniques," in *Proc. IEEE PESC'98*, Fukuoka, Japan, May 1998, pp. 172–178.

- [20] Y. H. Lee, R. Y. Kim, and D. S. Hyun, "A novel SVPWM strategy considering DC-link balancing for a multi-level voltage source inverter," in *Proc. IEEE APEC'98*, 1998, pp. 509–514.

- [31] K.A Corzine, and Y.L Familiant, "A New Cascaded Multilevel H-Bridge Drive," IEEE Trans. Power.Electron., vol.17, no.1, pp.125-131. Jan 2002.

- [32] R.Teodorescu, F.Blaabjerg, J.K.Pedersen, E.Cengelci, and P.N.Enjeti, "Multilevel Inverter by cascading industrial VSI," IEEE Trans. Ind. Electron., vol.49, no.4, pp.832-838. Aug.2002.

- [33] B.P.McGrath and Holmes, "Multicarrier PWM strategies for multilevel inverter," IEEE Trans.Ind.Electron., vol.49, no.4, pp.858-867. Aug.2002.