# A Review on Design and Implementation of Digital PLL for Clock Generation

Jayati Shukla, Saima Ayyub, Paresh Rawat

Research Scholar, Assistant Professor, Associate Professor& HOD

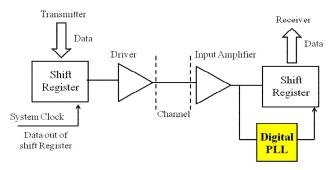

Abstract - The digital phase-locked loop, DPLL, is a circuit that is used frequently in modern integrated circuit design. Consider the waveform and block diagram of a communication system, Digital data1 is loaded into the shift register at the transmitting end. The data is shifted out sequentially to the transmitter output driver. At the receiving end, where the data may be analog (and, thus, without well-defined amplitudes) after passing through the communication channel, the receiver amplifies and changes the data back into digital logic levels. The next logical step i n this sequence is to shift the data back into a shift register at the receiver and process the received data. However, the absence of a clock signal makes this difficult. The DPLL performs the function of generating a clock signal, which is locked or synchronized with the incoming signal. The generated clock signal of the receiver clocks the shift register and thus recovers the data. This application of a DPLL is often termed a clock-recovery circuit or bit synchronization circuit. This paper basically reviews the design and implementation of DLL.

Keywords- DPLL, Clock generator, VCO, SoC, Charge pumps, PFD, Oscillator.

# 1. INTRODUCTION

Digital Phase locked loop is a mixed signal analog integrated circuit. Digital PLL is the heart of many communication as well as electronic systems. Mostly a higher lock PLL range with lesser locking time and should have tolerable phase noise. The most versatile application of a digital PLL is for clock generation or synchronization, clock recovery, communication systems and frequency synthesizers. In high performance digital systems like processors digital PLL or DPLL are commonly used to generate well timed on chip clock signals. Modern RF circuits or wireless mobile communication systems use PLL for synchronization, timing based synthesis, skew and jitter reduction. Digital PLL is extensively used in advanced communication systems, electronic and medical instrumentation systems. The PLLs are an integrated part of larger circuits on a single chip.

Phase-locked loops are widely employed in radio, telecommunications, computers and other electronic applications. They can be used to demodulate a signal, recover a signal from a noisy communication channel, generate a stable frequency at multiples of an input frequency (frequency synthesis), or distribute precisely timed clock pulses in digital logic circuits such as microprocessors. Since a single integrated circuit can provide a complete phaselocked-loop building block, the technique is widely used in modern electronic devices, with output frequencies from a fraction of a hertz up to many gigahertz.

Figure.1. Block Diagram of a communication system using DPLL

Strong interest in the implementation and design of digital PLLs (DPLL) started because of the popularity of large scale integrators (LSIs) [1]. Aside from the obvious advantages associated with digital systems, a digital version of PLL alleviates some of the problems associated with its analog counterpart; namely:

- 1. Sensitivity to dc drift and component saturation.

- 2. Difficulty in building higher order loops.

- 3. Need for initial calibration. [4]

# I. CLASSIFICATION OF PLL

There are many types of design which were proposed earlier. The broad classification of PLL Design is presented in Table 1. Any PLL is designed by modifying one of three stages phase detector, loop filter, voltage controlled oscillator.

A PLL is a device which locks an output signal phase relative to an input reference signal phase. PLL's are typically divided into broad categories listed.

In addition, with the ability to perform sophisticated signal processing on the IC chips, DPLL's are more flexible and versatile than analog PLL's [1]. The DPLL is still a semi analog circuit and is referred to as hybrid PLL. The all digital PLL (ADPLL) and software PLL has recently gained

increased attention. The ADPLL is built entirely from logic circuits and has replaced the classical DPLL in many applications, especially digital communications [1].

## Table 1

**Classification of PLL Categories**

| S.No. | PLL                         | Phase<br>Detector | Loop<br>Filter | Oscillator                                     |

|-------|-----------------------------|-------------------|----------------|------------------------------------------------|

| 1.    | Linear PLL or<br>Analog PLL | Analog            | Analog         | Voltage<br>Controlled<br>Oscillator<br>(VCO)   |

| 2.    | Digital PLL                 | Digital           | Analog         | Voltage<br>Controlled<br>Oscillator<br>(VCO)   |

| 3.    | Digital PLL                 | Digital           | Digital        | Digitally<br>Controlled<br>Oscillator<br>(DCO) |

| 4.    | Software PLL                | Software          | Softwar<br>e   | Software                                       |

# II. DESIGN

PLL: A basic PLL is a negative feedback system that receives an incoming oscillating signal and generates an output waveform that exerts the same phase/frequency relationship as the input signal. This is achieved by constantly comparing the phase of output signal to the input signal with a phase/frequency detector (PFD).

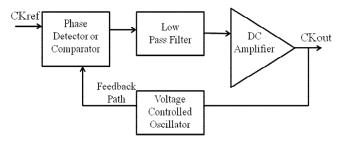

A PLL is a closed-loop feedback system that sets fixed phase relationship between its output clock phase and the phase of a reference clock. A PLL is capable of tracking the phase hangs that falls in this bandwidth of the PLL. A PLL also multiplies a low-frequency reference clock CKref to produce a highfrequency clock CKout this is known as clock synthesis. A PLL has a negative feedback control system circuit. The main objective of a PLL is to generate a signal in which the phase is the same as the phase of a reference signal. This is achieved after many iterations of comparison of the reference

In general a PLL consists of five main blocks:

- 1. Phase Detector or Phase Frequency Detector (PD or PFD)

- 2. Charge Pump (CP)

- 3. Low Pass Filter (LPF)

- 4. Voltage Controlled Oscillator (VCO)

- 5. Divide by N Counter

Figure.2. Block Diagram of Digital PLL

The basic operation of PLL can be divided into 3 steps.

- 1. The phase detector catches the phase difference between two inputs and generates an error signal Vpd whose average value is linearly proportional to the phase difference.

- 2. A loop filter is then used to suppress the high frequency components of the phase detector output allowing the average value to control VCO frequency.

- 3. Oscillator generates an output signal whose frequency is a linear function of the control signal out of the loop filter.

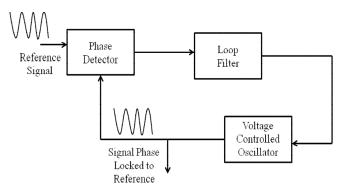

Figure.3 Basic block diagram of PLL(Analog or Digital)

Figure 3 shows the waveform of the reference signal and PLL output when loop is locked.

The generated signal is feedback to the input of the phase detector and another phase comparison is started until the phase difference achieves a fixed relationship [3][5].

## **III. DIGITAL PLL DESCRIPTION**

A PLL is comprised of a phase/frequency detector (PFD), charge pump (CP), a low-pass filter (LPF), and a voltagecontrolled oscillator (VCO). An input reference frequency (FREF) is sent to one of the PFD inputs. The other input terminal of PFD is driven by a divided version of VCO output signal to provide a negative feedback to the loop. The PFD detects differences in phase and frequency between the reference and feedback inputs to generate compensating up (UP) or down (DN) signals.

If reference input (FREF) occurs before that of feedback input (FBK), indicating that the VCO is running too slowly, the PFD produces a UP signal that lasts until the rising edge of the FBK. If the FBK occurs before FREF, the PFD produces a DN signal that is triggered on the rising edge of the FBK input and lasts until the rising edge of FREF. If the FBK frequency is less than that of FREF, the pulse-width of the UP signal is greater than the width of DN signal and vice versa. In this way, the PFD produces control signals that are unique for any phase and frequency relationship between reference and feedback signal.

These control signals are then passed through CP and a loop filter to generate a control voltage (Vctrl), which feeds into a VCO, the frequency of which is dependent on the control voltage input. Thus, based on phase/frequency relationship of input and feedback signal, the VCO can be forced to run faster or slower, which finally locks to oscillate at a fixed frequency once two inputs at PFD are phase/frequency aligned. The output of the VCO is an internally generated oscillator waveform. At steady state, the PLL system frequency is: The PLL is designed to operate within a limited band of input frequencies. If FREF is outside the defined band, circuit will not lock, thus FVCO will be different than expected one.

FPLL = FVCO = FREF \* P

Where:

FPLL = PLL frequency

FREF = Reference frequency

P = Feedback divider

The range of FREF from Fmin to Fmax where the PLL remains in locked condition is called the lock range of the PLL. Out of lock range (i.e., Fmax < Fref < Fmin), the PLL becomes unlocked. When the PLL is unlocked, the VCO oscillates at the frequency Ffr, called the free-running frequency of VCO. The PLL can achieve the lock again if FREF gets close enough to Ffr. This narrow band ( $\Delta$ Fc) of frequency, centered at Ffr so that the initially unlocked PLL acquires the lock again, is called the 'capture range of the DPLL.

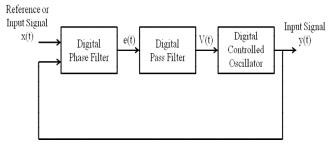

Figure.4 Block diagram of a Simple DLL

PLL has three operating states: - free running, capture and lock. In free running state, the feedback loop is open and there is no

external input frequency, the VCO oscillates at the natural frequency. In the capture state, an external input signal is necessary and feedback loop should be complete. PLL is in process of acquiring frequency lock in capture state. In lock state, the output frequency of VCO is locked onto the frequency of external input signal.

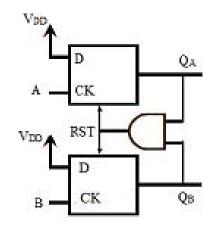

Digital PLL consists of Digital phase detector, analog loop filter, voltage controlled oscillator. Digital phase detector is shown in Figure. 4 where A is input signal tx and B is feedback signal through tx. As shown in Figure. 4, if A=1 then QA=1 and if at the same time B=1, then QB=1. Output of AND gate is connected to RESET pin when both are 1 and vice- versa. The e(t) is (QA– QB) and is used to detect difference between the phase and frequency. Filters are used after charge pump to reduce the ripple as shown in Figure. 5. Charge pump converts phase/frequency detector (PFD) logic states into analog signal suitable for voltage controlled oscillator [7].

Figure.5 Digital Phase/ Frequency Detector

# **IV. Architecture of PLL**

The architecture of a charge-pump PLL is shown in Figure 4. A PLL comprises of several components. They are (1) phase

or phase frequency detector, (2) charge pump, (3) loop filter, (4) voltage-controlled oscillator, and (5) frequency divider.

## A) Phase frequency Detector

The "Phase frequency Detector" (PFD) is one of the main part in PLL circuits. It compares the phase and frequency difference between the reference clock and the feedback clock. Depending upon the phase and frequency deviation, it generates two output signals "UP" and "DOWN". Figurebelow shows a traditional PFD circuit. the phase detector is basically a comparator. It compares the phase of external input

signal to the phase of VCO output signal. The phase comparator produces an error voltage e(t) which is due to difference in phase between two signals as shown in Figure. 2. It is used to determine when VCO and reference signal are aligned [3][6].

If there is a phase difference between the two signals, it will generate "UP" or "DOWN" synchronized signals. When the reference clock rising edge leads the feedback input clock rising edge "UP" signal goes high while keeping "DOWN" signal low. On the other hand if the

feedback input clock rising edge leads the reference clock rising edge "DOWN" signal goes high and "UP" signal goes low. Fast phase and frequency acquisition PFDs [6-7] are generally preferred over traditional PFD.

# B) Charge Pump and Loop Filter

Loop filter [1][3][5][6] is used to remove high frequency of the phase detector output and then applied to the input of VCO. Based on the property of PLL, the loop filter is made using low pass filter (LPF). It has to pass only the DC component and block the AC components.

Charge pump circuit is an important block of the whole PLL system. It converts the phase or frequency difference information into a voltage, used to tune the VCO. Charge pump circuit is used to combine both the outputs of the PFD and give a single output which is fed to the input of the filter. Charge pump circuit gives a constant current of value IPDI which should be insensitive to the supply voltage variation [8]. The amplitude of the current always remains same but the polarity changes which depend on the value of the "UP" and "DOWN" signal. The schematic diagram of the charge pump circuit with loop filter is shown in the Figure below

When the UP signal goes high M2 transistor turns ON while M1 is OFF and the output current is IPDI with a positive polarity. When the down signal becomes high M1 transistor turns ON while M2 is OFF and the output current is IPDI

with a negative polarity. The passive low pass loop filter is used to convert back the charge pump current into the voltage. The filter should be as compact as possible [9].The output voltage of the loop filter controls the oscillation frequency of the VCO. The loop filter voltage will increase if Fref rising edge leads Fin rising edge and will decrease if Fin rising edge leads Fref rising edge. If the PLL is in locked state it maintains a constant value.

## C) VCO/DCO IN PLL

Electrical oscillators are used in all kinds of electronic systems. Oscillators that will be discussed in this paper will find its application in synchronization of control logic with various analog and digital integrated circuits. Oscillatory behavior is ubiquitous in all physical systems specially in memory and mixed signal integrated circuits, in frequency and communication systems. Oscillators are the prime requirements of circuits needing time references and also to synchronize operations. An ideal oscillator would provide perfect time reference i.e. a perfect periodic signal [1], but oscillators are corrupted by undesired noise.

A variety of Oscillators are available but the principle of operation, the frequency of oscillation, their fabrication with respect to different CMOS logics relative, process technologies and their performance in noisy environment is different from one class of oscillators to other.

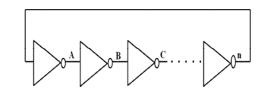

Figure.6. Ring Oscillator realization with n digital inverters

This ring oscillator is designed to be controlled in a oscillation frequency by a voltage input. The physical design of the very same will include C5 process, 300 nm process technology simultaneously various design rule checks and network consistency checks were performed. CMOS inverter ring oscillators offer numerous advantages like tuning ranges, signal swing and a small chip area.

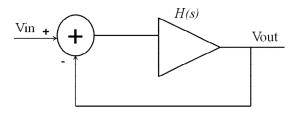

## C.1 BARKHAUSEN CRITERIA

The Barkhausen criterion is used to determine the oscillation startup condition. The Barkhausen stability criterion is necessary but not sufficient for oscillation[4].

$$|H(j \ge 1 \quad (i))|$$

$$\angle |H(j = \pi \quad (ii))|$$

The criteria for oscillation is not well understood, there is no known sufficient criteria for oscillation.

Them the circuit may oscillate at  $\mathbf{a}$  if the conditions (i) and (ii) are met called the Barkhausen criterion.

Figure.7 Generalized Feedback System[6]

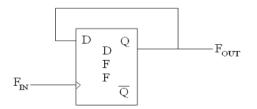

D) Frequency Divider

The output of the VCO is fed back to the input of PFD through the frequency divider circuit. The frequency divider in the PLL circuit forms a closed loop. It scales down the frequency of the

VCO output signal. A simple D flip flop (DFF) acts as a frequency divider circuit. The schematic of a simple DFF based divide by 2 frequency divider circuit is shown in the Figure below.

Figure.8 Schematic of a simple DFF based divide by 2 frequency divider circuit

## V. PERFORMANCE COMPARISONS

In this review[1], the proposed novel successive approximation algorithm to improve the frequency and phase locking time of BBPHD-based ADPLL without much scarification of output clock jitter. 790ns locking time demonstrates that such design is suitable for microprocessor, which needs to switch to a different frequency during dynamic frequency scaling. Although achieving fast-locking, it still needs to stall CPU during the locking process because the oscillator is reset and the frequency changes dramatically during SAR search. Therefore, future works will be to design an ADPLL that can both achieve fast locking and a smooth frequency change in DCO.

#### TABLE II

Performance Comparisons of DPLL Implementations with

respect to various process technologies [1]

| CMOS<br>Process<br>Technology | 180nm                | 130nm              | 65 nm               | 45 nm               |

|-------------------------------|----------------------|--------------------|---------------------|---------------------|

| Core Area                     | 0.14 mm <sup>2</sup> | $0.2 \text{ mm}^2$ | 0.07mm <sup>2</sup> | 0.07mm <sup>2</sup> |

| Power                         | 26.7 mW              | 16.5 mW            | 1.81 mW             | 16mW                |

| Output<br>Range               | 62-616<br>MHz        | 0.3-1.4<br>GHz     | 90-527<br>MHz       | 0.8-12<br>GHz       |

| Locking<br>Time               | NA                   | 3.5us              | NA                  | 46us                |

| Jitter RMS                    | 7.28ps               | 3.7ps              | 8.64ps              | 1.32ps              |

In this review[1], the proposed novel successive approximation algorithm to improve the frequency and phase locking time of BBPHD-based ADPLL without much scarification of output clock jitter. 790ns locking time demonstrates that such design is suitable for microprocessor, which needs to switch to a different frequency during dynamic frequency scaling. Although achieving fast-locking, it still needs to stall CPU during the locking process because the oscillator is reset and the frequency changes dramatically during SAR search. Therefore, future works will be to design an ADPLL that can both achieve fast locking and a smooth frequency change in DCO.

#### TABLE III

#### Performance Comparisons of ADPLL[2]

| Process               | 180 nm          | 180nm            |  |

|-----------------------|-----------------|------------------|--|

| Power<br>Consumption  | 26.7 mW         | 25.02 mW         |  |

| Resolution            | -               | 2.1 ps           |  |

| Jitter<br>Performance | 56 ps           | 32.86 ps         |  |

| Frequency<br>Range    | 62 MHz- 616 MHZ | 400 MHz- 860 MHz |  |

#### TABLE IV

#### Comparison of various technologies used in DPLL

| Technique               | Input<br>Frequency | Output<br>Frequency | Powe<br>r | Area                       |

|-------------------------|--------------------|---------------------|-----------|----------------------------|

| BW Tracking[11]         | 28 -225<br>MHz     | 1.80 GHz            | -         | -                          |

| Frequency<br>Estimation | 220 KHz- 8<br>MHz  | 28 – 446<br>MHz     | -         | 330x250<br>μm <sup>2</sup> |

| Algorithm for<br>fast locking[12]           |            |                  |             |                         |

|---------------------------------------------|------------|------------------|-------------|-------------------------|

| Delay based<br>technique[13]                | 12 MHz     | 2.40 GHz         | 12<br>mW    | 0.24<br>mm <sup>2</sup> |

| Adaptive loop<br>gain Control<br>(ALGC)[14] | 50 MHz     | 0.30-1.40<br>GHz | 16.50<br>mW | 0.20mm <sup>2</sup>     |

| Feed Forward<br>Compensation[15<br>]        | 376 MHz    | 4 to 416<br>MHz  | 11.39<br>mW | $\frac{2400}{\mu m^2}$  |

| Bang Bang<br>Algorithm [16]                 | 156.25 MHz | 40 GHz           | 46<br>mW    | 0.30<br>mm <sup>2</sup> |

| Auto Calibration [17]                       | 5-44 MHz   | 1.90-3.80<br>GHz | -           | 0.65mm <sup>2</sup>     |

| Digital<br>Calibration [21]                 | 26 MHz     | 1.80 GHz         | 41.6<br>mW  | 3.50mm <sup>2</sup>     |

In review [2], An all-digital PLL was proposed and designed with a tristate inverter delay cell based LPI-TDC using  $0.18\mu$ m CMOS process. The proposed delay-cell in LPI-TDC is exploited to obtain high performance and low power consumption. Other parts in the proposed ADPLL such as DLF and DCO are implemented to reduce jitter, and to generate a proper frequency through accurate digitized control words. The proposed ADPLL performs better than the conventional ones, and it will be a good reference for the future work.

## VI. CONCLUSION

In this paper a review for Digital PLL clock generator design and analysis is presented. The PLL circuit consumes a power of 11.9 mW from a 1.8 V D.C. The centre frequency of oscillation of the VCO depends upon the sizing of the transistors. The frequency deviation from the desired value can be reduced by properly choosing the transistor sizes.

## REFERENCES

- [1] Dian Huang, Ying Qiao, "A fast locked all digital phase locked loop for dynamic frequency scaling", Moon Seok Kim, Yong Bin Kim, Kyung Ki Kim, "All digital phase locked loop with local passive interpolation time to digital converter based on tristate inverter " IEEE transactions 2012.

- [2] Jaewook Shin and Hyunchol Shin, "A 1.9-3.8 GHz  $\Delta\Sigma$ Fractional-N PLL Frequency Synthesizer with Fast Auto-Calibration of Loop Bandwidth and VCOFrequency," IEEE Journal of Solid-State Circuits, Vol. 47, no.3, pp.665-675, Mar 2012.

- [3] Luca Vercesi, Luca Fanori, Fernando De Bernardinis, Antonio Liscidini and Rinaldo Castello, "A Dither-Less All Digital PLL for Cellular Transmitters,"IEEE Journal of Solid-State Circuits, vol 47, no.8, pp.1908-1920,Aug 2012.

- [4] Xin Chen, Jun Yang and Long-Xing Shi, "A Fast Locking All-Digital Phase-Locked Loop via Feed-Forward Compensation

Technique," IEEE Transactions on Very Large Scale Integration(VLSI) Systems, vol.19, no.5, pp.857-868, May 2011.

- [5] Chao-Ching Hung and Shen-Iuan Liu, "A 40-GHz Fast-Locked All-Digital Phase-Locked Loop Using a Modified Bang-Bang Algorithm," IEEE Transactions on Circuits and Systems-II, vol.58, no.6, pp.321-325, June 2011.

- [6] Ping-Hsuan Hsieh, Jay Maxey and Chih-Kong Ken Yang, "A Phase-Selecting Digital Phase-Locked Loop With Bandwidth Tracking in 65 nm CMOS Technology," IEEE Journal of Solid-State Circuits, vol. 45, no.4, pp.781-792, April 2010.

- [7] Ping-Hsuan Hsieh, Jay Maxey and Chih-Kong Ken Yang, "A Phase-Selecting Digital Phase-Locked Loop With Bandwidth Tracking in 65 nm CMOS Technology," IEEE Journal of Solid-State Circuits, vol. 45, no.4, pp.781-792, April 2010.

- [8] Liangge Xu, Saska Lindfors, Kari Stadius and Jussi Ryynanen, "A 2.4-GHz Low-Power All-Digital Phase-Locked Loop," IEEE Journal of Solid-StateCircuits, vol.45, no.8, pp.1513-1521, Aug 2010.

- [9] Deok-Soo Kim, Heesoo Song, Taeho Kim, Suhwan Kim and Deog-Kyoon Jeong, "A 0.3-1.4 GHz All-Digital Fractional-N PLL with Adaptive Loop GainController," IEEE Journal of Solid-State Circuits, Vol.45, no.11, pp.2300-2311, Nov 2010.

- [10] Quan Sun, Yonguang Zhang, Christine Hu-Guo, Kimmo Jaaskelainen and Yann Hu, "A fullyintegrated CMOS voltage regulator for supply-noise-insensitive charge pump PLL design,"Microelectronics Journal, Vol. 41, Issue 4, April 2010, Pages 240-246

- [11] S.J.Li, and H.H.Hsieh," A 10 GHz Phase-Locked Loop with a Compact Low-Pass Filter in0.18 μm CMOS Technology", IEEE Microwave and Wireless Components Letters, VOL. 19, NO. 10, OCTOBER 2009.

- [12] H.Janardhan, and M.F.Wagdy "Design of a 1GHz Digital PLL Using 0.18 μm CMOS Technology," IEEE Proc. of the Third International Conference on Information Technology, 2006.

- [13] R.E. Best, "Phase Locked Loops Design, Simulation and Applications," McGraw-Hill Publication, 5th Edition, 2003.

- [14] S.M.Kang, and Y.Leblebici, "CMOS Digital Integrated Circuits: Analysis and Design," McGraw-Hill Publication, 3 rd Edition, 2003.

- [15] R.J.Baker, H.W.Li, and D.E.Boyce, "CMOS Circuit Design, Layout, and Simulation," IEEE Press Series on Microelectronic Systems, 2002.

- [16] B. Razavi, "Design of Analog CMOS Integrated Circuits," Tata McGraw Hill Edition, 2002.

- [17] M.Mansuri, D.Liu, and C.K.Yang, "Fast Frequency Acquisition Phase Frequency Detectorfor GSamples/s Phase Locked Loops," IEEE Journal of Solid State Circuit, Vol. 37, No. 10,Oct., 2002.

- [18] Youngshin Woo, Young Min Jang and Man Young Sung, "Phase-locked loop with dualphase frequency detectors for high-frequency operation and fast acquisition," Microelectronics Journal, Vol. 33, Issue 3, March 2002, Pages 245-252.

- [19] S. M. Shahruz, "Novel phase-locked loops with enhanced locking capabilities," Journal ofSound and Vibration, Vol. 241, Issue 3, 29 March 2001, Pages 513-523.

- [20] Dan H. Wolaver, "Phase Locked Loop Circuit Design," Prentice Hall Publication, 1991.

# **AUTHOR'S PROFILE**

Jayati Shukla has received her Bachelor of Engineering degree in Electronics & Communication Engineering from Trinity Institute of Technology, Bhopal in the year 2012. At present she is pursuing M.Tech with the specialization of Embedded System & VLSI Design in Truba College of Science & Technology. Her area of interest includes Digital Electronics, VLSI Design, Control System.

**Saima Ayyub** B.E., M. Tech. She is Assistant Professor in Department of Electronics and Communication Engineering, TCST Bhopal. She has 06 years of academic experience. Her area of interest includes VLSI Design & Embedded System.

**Dr. Paresh Rawat** M.Tech, Ph.D. He is Associate Professor and HOD in Department of Electronics and Communication Engineering, TCST Bhopal. He has over 09 years of academic experience. His area of interest includes Digital Electronics, Digital Circuits System & Design.