# PWM Control Used for Switching of Interleaved Buck Converter

## Vineeta Shakya<sup>1</sup>, Shailendra Pawar<sup>2</sup>

<sup>1</sup>M.Tech SAMCET Bhopal, <sup>2</sup>A.P. C.I.S.T Bhopal

Abstract – This paper introduces PWM control used for switching Interleaved Buck Converter. Pulse Width Modulation is basis of many power Electronics Devices .The theoretically Zero rise and fall time of ideal PWM Waveform represent a preferred way of driving many semiconductor devices like Diode, Transistor and MOSFET. With the exception of certain converters most of the converters used in power electronic are controlled by PWM waveform. The rapid rising and falling edge of PWM signal turn on and turn of the semiconductor devices as fast as practically possible and it minimize the transition time and losses associated with it.

Keywords – Pulse width modulation control, Interleaved Buck Converter, Interleaved PWM.

#### **1. INTRODUCTION**

Pulse Width modulation is one of the most powerful techniques of controlling analog circuit with digital output of processor. PWM is mostly used in applications like measurement and communicating power control and power conversion. In this paper we are taking its application of controlling DC-DC converter. In which the PWM signal is used to convert unregulated DC voltage into regulated or variable DC voltage at its output. A PWM is signal is not constant always its main parameter is duty cycle (*D*).Duty cycle describe the part of ON Time on the regular interval.

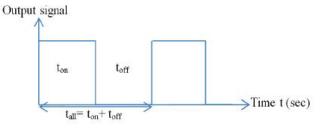

Thus the output signal is described by equation 1.1 and 1.2

Output Voltage = D \* Input Voltage(1.1)

$$Output Voltage = t_{ON} / T Input Voltage$$

(1.2)

Whwre 't' $_{\rm ON}$  represent on time of signal and 'T' is regular time interval.

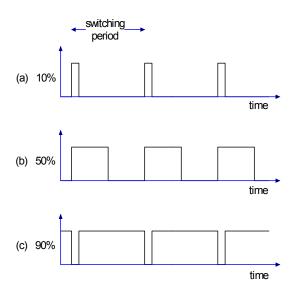

The ratio of ON time to switching period is the duty cycle. Duty cycle plays important role for controlling switching of semiconductor devices using PWM signal. Figure 1.2 shows three different variations of PWM duty cycle, 10%, 50% and 90%. Duty cycle D is the ration of On time over regular switching interval and given by equation 1.3.

Fig. 1.1 PWM with duty cycle

$$D = t_{\rm ON} / T \tag{1.3}$$

Whwre 't'<sub>ON</sub> represent on time of signal and 'T' is regular time interval.

Fig 1.2 PWM Waveforms for different duty cycles

## 2. TYPES OF PWM

Switching frequency plays an important role for defining PWM control Depending on frequency there is two types of PWM control signal (2.1)

onstant frequency PWM Control

ariable frequency PWM Control

2.1

#### **ONSTANT FREQUENCY PWM**

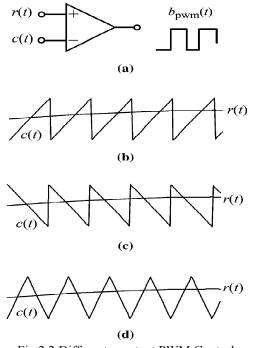

A constant-frequency (CF) PWM signal can be produces simply by comparing a reference voltage signal, r(t), with a carrier signal, c(t), as depicted in Figure. 2.1 a. The binary PWM output can be mathematically written as equation 2.1 where r(t) is reference voltage and c(t) is carrier signal and b<sub>PWM</sub> Pulse width modulation output is sign function of differences of these two signals. as given by equation 2.1

$b_{\text{PWM}}(t) = \text{sgn}[r(t) - c(t)]$ where 'sgn' is the sign function

There are three types of carrier signals are commonly used in constant-frequency PWM they are as follows:

- As shown in figure 2.1 (b) position of falling edge is modulated with the reference voltage. Whereas rising edge of output of PWM is occurred at fixed instant of time therefore this method is called constant frequency trailing edge modulation.

- 2. This modulation is opposite to trailing edge modulation. the falling edge appeared at fixed time instant while rising edge modulation change with reference signal. This method is called constant frequency leading modulation

- 3. Other method of Constant frequency modulation both the leading edge and falling edge are varies with the reference signal. the output of such modulation is triangular waveform this is called constant frequency double edge modulation. Figure 2.1 (c) referred to double edge modulations.

The Most common DC–DC converters are trailing-edge modulation. Double-edge modulation removes certain harmonic when the reference is a sinusoidal wave, and is preferred for AC–DC and DC–AC converters where the PWM reference has a sinusoidal component.

A blend of synchronized leading-edge and trailing-edge modulation is used to control a boost single-phase power factor correction (PFC) converter and a buck DC–DC converter to reduce ripple in the intermediate DC bus capacitor. To ignore many switching transition within a carrier cycle, the reference is first sampled at the point where the carrier reaches its highest and minimum value. This type of modulation is known by regular-sampling PWM. For distinguish from such sampled PWM, the analog version discussed earlier is also calles natural-sampling PWM. With a saw tooth or inverted saw tooth carrier, samples are taken at the starting of a carrier cycle

Fig 2.2 Different constant PWM Control

## 2.2 ARIABLE FREQUENCY PWM CONTROL

Variable-frequency (VF) PWM is not as popular as constant frequency (CF) PWM. VF-PWM allows the determination of duty ratio when switching period is known. There are three types of VF PWM are:

- (a) Constant OFF time, variable ON-time

- (b) Constant ON-time, variable OFF-time

- (c) Hysteretic control.

Constant OFF time and Constant ON-time modulators have advantages in term of low audio susceptibility, ease of implementation or lower power stage weight. Whereas hysteretic is favoured due to its simple design and high linearity.

## 2.2.1 CONSTANT OFF TIME VARIABLE ON TIME PWM

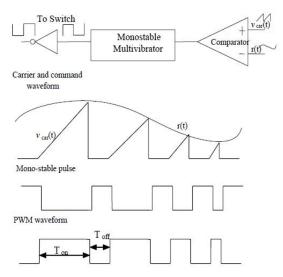

In this type of PWM control maintains the OFF time constant and ON time is determined in the beginning of each switching cycle. Control schemes and associated waveforms are shown by figure 2.3.

Fig 2.3Constant OFF time and Variable ON time PWM

Where  $v_{car}$  (t) is carrier signal and r (t) is command signal or reference signal.

In Constant OFF Time and Variable ON PWM both reference and carrier signals are applied to the OP-AMP which acts as the comparator circuit. The output of Comparator is given to the monostable multivibrator. The output of multivibrator is put inside the inverter which provides invert output as shown in figure 2.3.

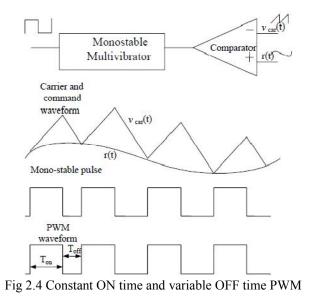

## 2.2.2 CONSTANT ON TIME VARIABLE OFF TIME PWM

In this case the duration in which switching device remains on is constant while the OFF time is determine at the end of switching cycle. Constant On time control schemes and wave form are displayed in figure 2.4

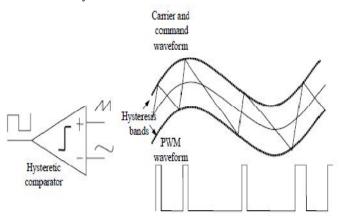

#### 2.2.3 HYSTERETIC CONTROL

In Hysteretic PWM output allowed to oscillate within the predefined band. This band is called hysteretic band. Figure 2.5 shows the hysteretic control and its waveforms.

Fig. 2.5 Hysteresis PWM control

## **3. GENERATION OF PWM SIGNAL**

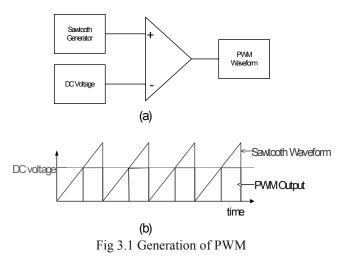

The generation of a pulse width modulation PWM signal can be achieved as shown in figure 3.1.

For generation of PWM signal first saw tooth wave form is generated and this saw tooth signal and constant DC Voltage are fed into an OP-AMP. Both signals are compared. This is shown in figure 3.1(a)

When the saw tooth signal is less than the DC voltage, the output of the comparator is a logic '0', and when the saw tooth signal is greater than the DC voltage, the output of the comparator is a logic '1'. Figure 3.1(b) shows how the PWM waveform is generated by comparing the DC voltage with the saw tooth waveform.

## **L** VOLUME-13, NUMBER-02, 2016

## 4. INTERLEAVED PWM

IIITE

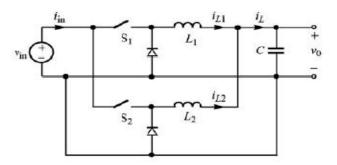

When the two PWM converters are connected in series or parallel circuit is known as interleaved PWM. These type of circuit have many advantages like all converters into a same circuit can be operate at same frequency but have different phase difference to each other. This technique of interleaving is very widely used in power electronics applications.

Fig 4.1 Two buck converters connecting in parallel

The advantage of interleaving is best understood by the figure 4.1. In this figure two identical buck converter are connected in parallel and they can work on same input output voltage. Both converters are operated on same carrier frequency but have different phase shift. The resultant ripple obtained by the converter is shown in figure 4.2 below the output voltage is assumed to be constant and both inductors  $L_1$  and  $L_2$  are assume to be identical. From the figure it is seen that the output current  $i_L$  has very small ripples and output capacitor is charged by this current  $i_L$ . We can also decreases the ripple by keep the value of duty ratio is kept 0.5. Similar effect can be seen in waveform of two paralleled buck converter. Same technique is applied to DC-DC converters.

In general If 'N' identical converter are connecting in parallel all converter will have phase shift of each other by the 'N' shift of carrier cycle then the fundamental frequency of combined input current is  $Nf_C$  where  $f_C$  is carrier frequency of individual converter. This reduction in ripple can reduce the requirement of costly filter

Response of each inductor used in buck converter can be written by equation 4.1 and 4.2

$$L_1 \frac{d}{dt} i_{L1} = v_{in} s_1(t) - v_0 \tag{4.1}$$

$$L_2 \frac{d}{dt} i_{L2} = v_{in} s_2(t) - v_0 \tag{4.2}$$

Where  $s_1(t)$  and  $s_2(t)$  is switching function of  $S_1$  and  $S_2$ .

Assuming L1 and L2 are equal to L we can obtain the response of combined current which is written in equation 4.3.

$$L\frac{d}{dt}i_{L} = v_{in}[s_{1}(t) + s_{2}(t)] - 2v_{0}.$$

(4.3)

Equation 4.3 shows the cancellation of harmonic in current  $i_L$  this cancellation in the  $i_L$  is due to cancellation in PWM harmonics.

$s_{1}(i)$   $s_{1}(i)$   $s_{2}(i)$   $i_{l1}$   $i_{l2}$   $i_{l2}$   $i_{l2}$   $i_{l1}$   $i_{l2}$   $i_{l2}$

Fig 4.2 Output waveform of Interleaved PWM Converter

Figure 4.2 shows ripple cancellation effect of interleaving. By these interleaving techniques we can reduce the harmonics in output voltage up to very high instant. Therefore interleaving technique provides very highly regulated output.

## SIMULATION/EXPERIMENTAL RESULTS

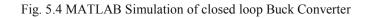

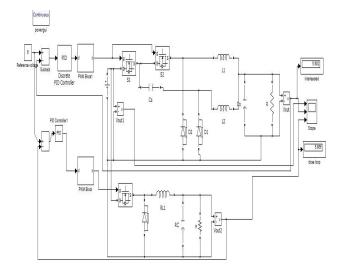

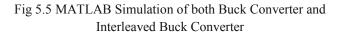

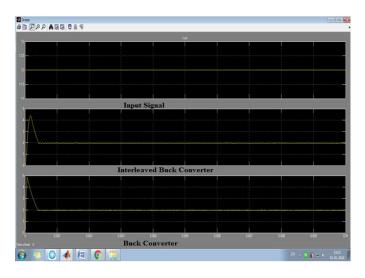

Simulation of Buck converter is done by MATLAB and following result were obtained

## Fig 5.1 Open loop Buck converter using PWM Control

|        | 2                                      | 1                                                                                                                |                                                                                                                      |               |

|--------|----------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------|

|        |                                        | 1                                                                                                                | 1                                                                                                                    |               |

|        |                                        |                                                                                                                  |                                                                                                                      |               |

| -//pum | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | and the second | and and the second s<br>: | مر مرمرمرمن م |

| L      |                                        |                                                                                                                  |                                                                                                                      |               |

|        |                                        |                                                                                                                  |                                                                                                                      |               |

| T      |                                        |                                                                                                                  |                                                                                                                      |               |

| V      |                                        |                                                                                                                  |                                                                                                                      |               |

Fig 5.2 MATLAB Simulation of Buck converter with PWM control

Fig 5.3 Closed Loop Buck Converter

| 1           |        |    |          |  |

|-------------|--------|----|----------|--|

|             |        | l. |          |  |

| L. <u>A</u> |        |    | <u>k</u> |  |

|             |        |    |          |  |

|             |        |    |          |  |

|             |        |    |          |  |

|             |        | ÷  |          |  |

| H           | ······ |    |          |  |

|             |        |    | ;        |  |

| +           |        |    |          |  |

| /           |        | į. |          |  |

| /           |        |    |          |  |

Fig. 5.6 Comparative resultant wave form of Buck Converter and Interleaved Buck Converter

| Table 1 : Parameter used in simulation of Interleaved |  |  |  |  |

|-------------------------------------------------------|--|--|--|--|

| <b>Buck Converter using PWM Control</b>               |  |  |  |  |

| Vd         | 24V              |

|------------|------------------|

| L          | 4.215mH          |

| С          | 1000µF           |

| RL         | 1.1 Ω            |

| PID        | Kp = 6, Ki =1,Kd |

|            | = 0.0001,        |

| Vref       | 5V               |

| duty ratio | 0.65             |

#### 6. CONCLUSION

The computer simulation and Results, it is seen that the Pulse width modulation control provides better control signal for interleaved buck converter for both open loop converter and closed loop converter because it changes its state (switch on and switch off) very quickly to the semiconductor switch. When we used interleaved PWM for same switching frequency it reduces the output ripples and this technique also reduces the requirement of costly filters in power supplies.

## REFERENCES

- [1] W. Yan, C. Pi, W. Li, and R. Liu, "Dynamic dead-time controller for synchronous buck DC-DC converters," *Electronics Letters*, vol. 46, no. 2, pp. 164-165, Jun. 2010.

- [2] S. Köse and E. G. Friedman, "An area efficient fully monolithic hybrid voltage regulator," in *Proc. IEEE International Symposium on Circuits and Systems*, May 2010, pp. 2718-2721.

- [3] Y.-T. Lee, C.-L. Wei, and C.-H. Chen, "An integrated stepdown DC-DC converter with low output voltage ripple," in *Proc. IEEE Conference on Industrial Electronics and Applications*, Jul. 2010, pp. 1373-1378.

- [4] A. Emira, H. Elwan, and S. Abdelaziz, "DC-DC converter with on-time control in pulse-skipping modulation," in *Proc. IEEE International Symposium on Circuits and Systems*, Aug. 2010, pp. 2746-2749.

- [5] R. C.-H. Chang, H.-M. Chen, C.-H. Chia, and P.-S. Lei, "An exact current-mode PFM boost converter with dynamic stored energy technique," *IEEE Transactions on Power Electronics*, vol. 24, no. 4, pp. 1129-1134, Apr. 2009.

- [6] M. D. Mulligan, B. Broach, and T. H. Lee, "A 3MHz low-voltage buck converter with improved light load efficiency," in *Proc. IEEE International Solid-State Circuits Conference*, Feb. 2007, pp. 528-620.

- [7] P. Y. Wu and P. K. T. Mok, "A monolithic buck converter with near-optimum reference tracking response using adaptiveoutput-feedback," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 11, pp. 2441-2450, Nov. 2007.

- [8] F.-F. Ma, W.-Z. Chen, and J.-C. Wu, "A monolithic currentmode buck converter with advanced control and protection circuits," *IEEE Transactions on Power Electronics*, vol. 22, no. 9, pp. 1836-1846, Sep. 2007.